- ロボット・自動装置・産業用IT

- 自動装置

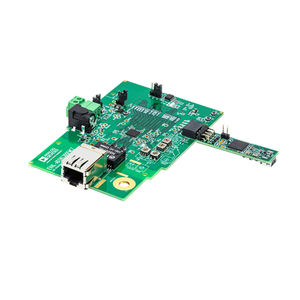

- イーサネットトランシーバー

- ADI/リニアテクノロジー

イーサネットトランシーバー ADIN1200 seriesデータアナログ

お気に入りに追加する

商品比較に追加する

特徴

- ネットワーク

- イーサネット

- 有効範囲 / 出力

- データ, アナログ

詳細

10BASE-Te/100BASE-TX IEEE® 802.3™準拠

MII、RMII、およびRGMII MACインターフェース

100BASE-TX RGMII遅延送信:<124ns、<250nsの受信

100BASE-TX MII遅延送信:<52ns、<248nsの受信

EMC試験規格

IEC 61000-4-5サージ(±4kV)

IEC 61000-4-4電気高速トランジェント(EFT)(±4kV)

IEC 61000-4-6伝導耐性(10V)

EN55032放射妨害波(クラスA)

EN55032伝導放射(クラスB)

マルチレベル・ピン・ストラップを使用した非管理構成

IEEE 802.3azに準拠したEEE

IEEE 1588タイム・スタンプ・サポートのためのパケット開始検出

リンク検出の性能向上

設定可能LED

水晶発振器/クロック入力:25MHz

25MHz/125MHz同期クロック出力

小型パッケージと広い動作温度範囲

32ピン、5mm × 5mm LFCSP

−40°C~+105°Cおよび−40°C~+85°Cの周辺運用で仕様規定

低消費電力

100BASE-TXで139mW

3.3V/2.5V/1.8V MACインターフェースVDDIO電源

単電源動作:3.3V VDDIO

電源モニタとPORを内蔵

ADIN1200は、低遅延仕様の低消費電力、単一ポートの10/100Mbpsイーサネット・トランシーバーで、産業用イーサネット・アプリケーション向けに設計されています。

この設計は、Energy Efficient Ethernet(EEE)物理層デバイス(PHY)コアと、関連するすべての一般的なアナログ回路、入出力クロック・バッファリング、マネージメント・インターフェース、サブシステム・レジスタ、メディア・アクセス制御(MAC)インターフェース、リセット/クロック制御およびピン配置を管理するためのコントロール・ロジックを内蔵しています。

ADIN1200は、5mm × 5mmの32ピン・リード・フレーム・チップ・スケール・パッケージ(LFCSP)を採用し、3.3V MACインターフェース電源を使用すると想定して、3.3Vの単電源で動作することができます。システム・レベルでの設計で最大限の柔軟性を得るために、独立したVDDIO電源を使用して管理データ入出力(MDIO)およびMACインターフェース電源電圧をADIN1200上の他の回路から独立して構成することで、1.8V、2.5Vまたは3.3Vで動作することができます。パワーアップ時、各電源が最小立上がり閾値を上回り、電源が良好であると見なされるまで、ADIN1200はハードウェア・リセット状態が保たれます。電圧低下に対しては、電源を監視して1個以上の電源が立下がり閾値を下回っていないかを検出し、下回っていた場合は電源が戻ってパワー・オン・リセット(POR)回路を満たすまでデバイスをハードウェア・リセット状態に保つことで保護されています。

MIIマネージメント・インターフェース(MDIOインターフェースとも呼ばれます)は、ホスト・プロセッサまたはMACとADIN1200の間に2線式シリアル・インターフェースを提供し、PHYコア・マネージメント・レジスタで制御情報とステータス情報へのアクセスを可能にします。インターフェースは、IEEE® 802.3™規格の条項22と条項45の両方の管理フレーム構造に準拠しています。

カタログ

この商品のカタログはありません。

ADIの全カタログを見る