- Electricity - Electronics

- Electronic Component

- geb-enterprise

- Products

- Catalogs

- News & Trends

- Exhibitions

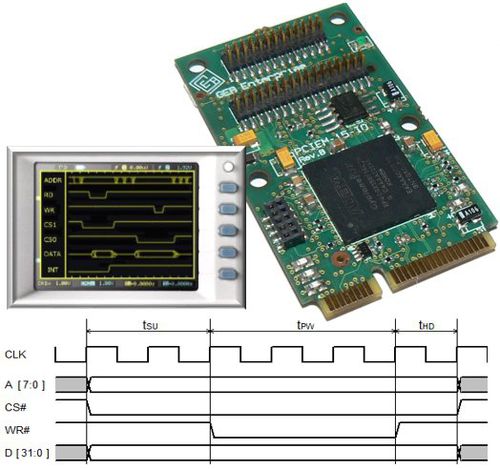

PCI Express bridge GPIO-BUS MS64-Windows| 141030-01A1

Add to favorites

Compare this product

Description

The IOBUS IP is a dynamically reconfigurable asynchronous bus master designed by GEB Enterprise. It supports 8/16/32 Data Bus wide, external interrupts, either fixed latency or variable latency bus cycle.

The IOBUS shall be the bus used for communication between a master (the Pcie card) and an unspecified number of slaves. The bus supports up to 32 Data bits, up to 8 bits address, 2 Chip Select (CS#), Read Enable(RD#), Write Strobe (WR#), Interrupt request (INT#) and an optional Wait signal (WAIT#).

On the internal bus side, the IOBUS IP is full compliant with the Altera Avalon Specification, so it can be easily added to any Altera Qsys design. On this side, there are two Avalon Slave Interface, the first one is labeled MEM allows acces to external devices. The second interface is labeled CSR, it implements a configuration space registers that must be used to programming the timings. The CSR allows programming of setup (ts), pulse width (tpw), hold time (th) selectively for Read and Write cycles and also the user can also enable both the interrupt request and the wait signals and their polarity.

*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.